SpacemiT unveils its K3 RISC-V AI CPU built on a fully open architecture, aiming to bring power-efficient, on-device AI and reduce dependence on proprietary x86 and ARM platforms.

Chinese RISC-V chipmaker SpacemiT has launched the K3 AI CPU, a new processor built on the open-source RISC-V instruction set architecture and designed for intelligent terminals and edge AI computing rather than servers or GPUs. The chip combines general-purpose processing with native AI acceleration to deliver a flexible, power-efficient and cost-effective alternative to closed x86 and semi-open ARM ecosystems.

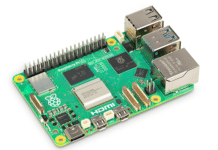

RVA23-compliant, K3 integrates eight X100 RISC-V cores clocked up to 2.4GHz, supports 1024-bit vector extensions and native FP8 precision, and delivers up to 60 TOPS of AI compute. It supports 32GB LPDDR5 memory, runs 30–80B parameter models on a single chip, and operates within a 15–25W power envelope.

A hardware–software co-design approach enables compatibility with Triton, TileLang, major open-source AI frameworks and Linux distributions, including Ubuntu, OpenHarmony and OpenKylin. SpacemiT is also opening hardware reference designs to developers and system integrators.

“We believe the long-term direction of computing architectures is a transition from closed to open systems. x86 is highly closed, Arm is semi-open, while RISC-V is fully open. In the long run, open instruction sets are more likely to become the foundation of global computing,” said Chen Zhijian, Founder and CEO of SpacemiT.

The company’s previous K1 has shipped over 150,000 units across robotics and industrial control deployments. With orders already secured, K3 deliveries begin in April 2026.

While RISC-V still trails x86 and Arm in high-end scale, the launch signals China’s push to move open-source hardware from experimentation to production-ready edge AI.