- The European funded project MEEP brings together BSC, UNIZG-FER, and TÜBİTAK BILGEM to build the next generation open source software and hardware.

- The project will run for three years with a budget of €10.3 million, of which €5.15 million is directly funded by the European Union.

Launched on January 01 and coordinated by the Barcelona Supercomputing Center (BSC), the European project “MareNostrum Experimental Exascale Platform” (MEEP) backs the objective of the European Union program EuroHPC to make competitive European technology integrated into future exascale supercomputers.

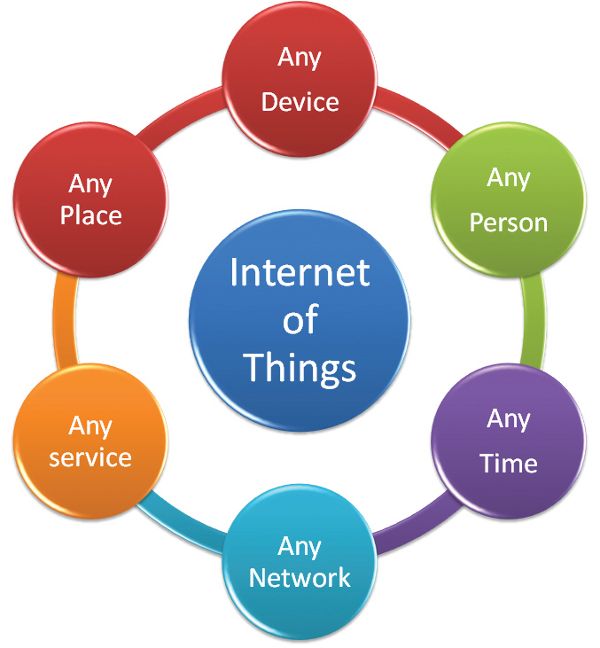

Particularly, it intends to build an exploratory supercomputing infrastructure for the development, integration, testing, and co-design of a broad range of European technologies that could become a part of the future European exascale systems. The supreme ambition is to develop an open full-stack (software and hardware) ecosystem that could become the grounds for other European systems, both in high-performance computing (HPC) and embedded computing, with advantages for numerous stakeholders within industry and academia.

“The MareNostrum Experimental Exascale Platform (MEEP), as performance evaluation and software development vehicle for future chip designs, will provide European technology that will set a foundation for many systems, both in HPC and beyond,” says John Davis, MEEP coordinator at BSC. “By championing the open-source RISC-V instruction set architecture, MEEP will help ensure European technological sovereignty by avoiding the export restrictions associated with proprietary models, while building the software ecosystem necessary to make RISC-V viable for a wider range of applications.”

Using an advanced emulation platform based on field-programmable gate arrays (FPGAs), MEEP will offer a testbed for RISC-V-based infrastructure. MEEP’s software development will transform into a proof-of-concept for industrial utilisation, permitting next-generation exploration of computer architecture as well as software development of existing and future HPC applications, including emerging artificial intelligence workloads, throughout fields from automotive to pharmaceutical.

“By experimenting with RISC-V-based hardware designs through FPGA emulation, we can fine-tune the right architectures before committing to silicon,” adds Peter Hsu, MEEP director at BSC. “The emulation platform will also allow us to test the full stack, from applications to hardware.”

With funding from European organisations, MEEP will run for three years with a budget of €10.3 million, of which €5.15 million is directly funded by the European Union. So that it fulfils its ambitions, MEEP brings together three European Union (EU) partners: BSC (Spain), as coordinator, will make available hardware and software along with expertise to build infrastructure for European chip developing targeting exascale machines, UNIZG-FER (Croatia) will provide its proficiency in architecture and building and deploying FPGA-based systems, and TÜBİTAK BILGEM (Turkey) which will contribute by offering deep expertise in architecture, verification, and advanced logic design.