RISC-V International, the open hardware standards organisation, announced that RISC-V members have approved 15 new specifications – resenting more than 40 extensions – for the free and open RISC-V instruction set architecture (ISA).

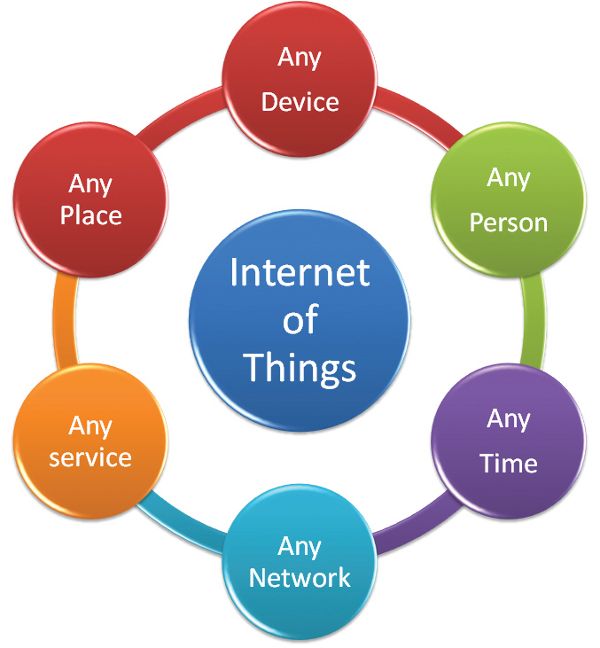

Most notably, RISC-V members approved the vector, scalar cryptography, and hypervisor specifications which will help unlock new opportunities for developers creating RISC-V applications for artificial intelligence (AI) and machine learning (ML), the Internet of Things (IoT), connected and autonomous cars, data centres, and more.

According to the organisation, the Vector specification will help accelerate the computation of data intensive operations like ML inference for audio, vision, and voice processing. With RISC-V Vector, developers can process complex data arrays and scalar operations quickly and with low latency.

The simplicity and flexibility of Vector allows companies to easily customise RISC-V solutions for a wide variety of edge computing applications from consumer IoT devices to industrial ML applications.

The RISC-V Hypervisor specification is said to virtualise supervisor-level architecture to host guest operating systems atop a type-1 or type-2 hypervisor. Virtual machine implementations require the RISC-V Hypervisor specification. The Hypervisor specification will help drive RISC-V adoption in cloud and embedded applications where virtualisation is critical, such as in data centres, automotive applications, and industrial control applications.

The RISC-V community has ported KVM and other open source Virtual Machines on top of simulators using the new specification.

The RISC-V Scalar Cryptography specification enables the acceleration of cryptographic workloads for small footprint deployments. These extensions significantly lower the barrier to entry for secure and efficient accelerated cryptography in IoT and embedded devices.