OpenHW introduced an advanced DevKit which boosts IoT, embedded, and AI-driven projects with good efficiency, seamless AWS connection, and a powerful eFPGA, Join the revolution.

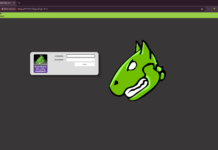

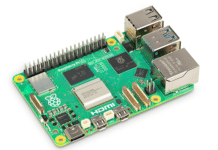

OpenHW Group has unveiled a development Kit for an open-source reduced instruction set computer (RISC-V) microcontroller unit ( MCU), which is now up for orders. This DevKit comes with an open-source printed circuit board (PCB) that embeds the processor from OpenHW and multiple peripherals. It offers a software development kit (SDK) with a robust eclipse-based integrated development environment (IDE). It provides a seamless connection to Amazon Web Services (AWS) through AWS IoT ExpressLink, ensuring secure and dependable interactions between IoT devices and AWS cloud platforms.

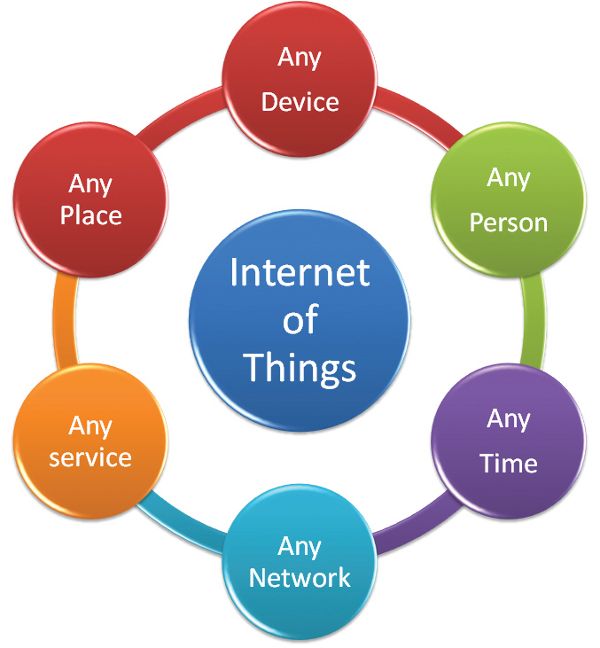

This kit enables software development for embedded, IoT, and artificial intelligence (AI)-driven applications. It is based on the open-source CV32E40P embedded-class processor, a small, efficient, 32-bit, in-order open-source RISC-V core with a four-stage pipeline that implements the RISC instruction extensions. It is designed to streamline the software development process for various applications, including those in the embedded systems domain, the Internet of Things (IoT), and applications driven by artificial intelligence (AI). At the heart of this kit is the open-source CV32E40P embedded-class processor. This processor is distinct in its design, being a compact yet highly efficient 32-bit in-order processor that belongs to the open-source RISC-V family. The core is designed with a four-stage pipeline, engineered to fully implement the RISC instruction extensions, providing an optimal blend of performance and efficiency for developers.

The SDK included in this package has an IDE, a debugger, a GCC compiler, the FreeRTOS real-time operating system, and demonstration software. This initiative underscores the collective development of high-quality, open-source CORE-V processor IP, supplemented by both hardware and software, brought to fruition through the collaborative efforts of a diverse array of members from across the industry.

The burgeoning ecosystem united to present the kit tailored for IoT developers. It allows the merging of digital and analog signals on a single chip, offering affordable and efficient performance for connected, low-power applications. The processor’s design and verification drew significant input from entities like Imperas, Siemens EDA, and SiLabs, rooted in the PULP Platform’s RI5CY core. It features an eFPGA to boost AI/ML (Machine Learning) and other heavy-duty tasks.